#### General Description

The MAX3975 is a +3.3V driver designed to directly modulate common-anode vertical cavity surface emitting lasers (VCSELs) at data rates up to 10.7Gbps. The driver output can be connected directly to the VCSEL, requiring no external components for biasing. With a 2.5mm x 2.5mm chip-scale package (UCSP $^{\text{TM}}$ ), transmit disable, output-current monitor, and 0°C to +85°C operation, the MAX3975 is ideal for 850nm XFP/XENPAK transceivers

The MAX3975 delivers 3mA to 12mA of modulation current, with 1.5mA to 10mA of bias current (peak current 22mA). Typical switching time is 28ps (20% to 80%) with 8ps of deterministic jitter.

#### **Applications**

10 Gigabit Ethernet Transceivers XFP/XENPAK/X2/XPAK Optical Transceivers **SONET VSR Optical Transmitters** 10 Gigabit Fibre-Channel Transceivers

#### Ordering Information

| PART         | TEMP<br>RANGE | PIN-PACKAGE                   | PKG<br>CODE |

|--------------|---------------|-------------------------------|-------------|

| MAX3975UBA-T | 0°C to +85°C  | 20 UCSP-20<br>(2.5mm × 2.5mm) | B25-4       |

UCSP is a trademark of Maxim Integrated Products, Inc.

#### **Features**

- ♦ 2.5mm x 2.5mm Chip-Scale Package (5 x 5 Array UCSP)

- ♦ Single +2.97V to +3.63V Supply Voltage

- ♦ 28ps Switching Time

- **♦ DC-Coupled Output**

- ♦ 3mA to 12mA Modulation Current

- 1.5mA to 10mA Bias Current

- **♦ Output Disable Circuit**

- ♦ Output-Current Monitor

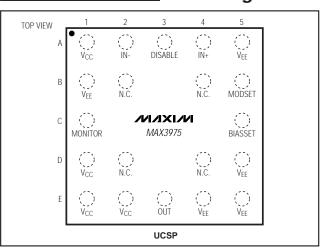

#### Pin Configuration

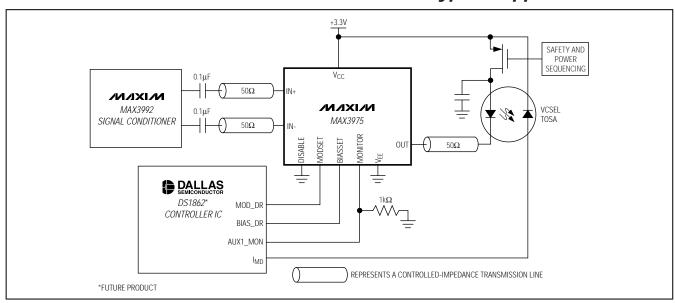

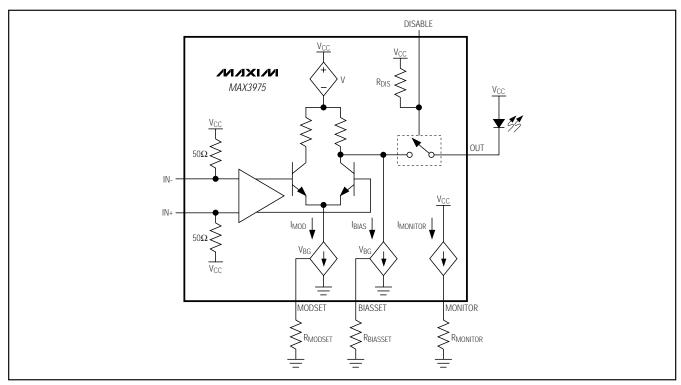

## Typical Application Circuit

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage at IN+, IN(V <sub>CC</sub> - 1.75V) to (V <sub>CC</sub> + 0.5V)  Differential Input Voltage (IN+ - IN-)±1.5V  Voltage at DISABLE+0.5V to (V <sub>CC</sub> + 0.5V) | Continuous Current at OUT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                               | SYMBOL                          | CONDITIONS                                                                          | MIN  | TYP  | MAX | UNITS             |

|-----------------------------------------|---------------------------------|-------------------------------------------------------------------------------------|------|------|-----|-------------------|

| POWER SUPPLY                            |                                 |                                                                                     |      |      |     |                   |

| Power-Supply Current                    |                                 | I <sub>BIAS</sub> = 10mA, I <sub>MOD</sub> = 12mA <sub>P-P</sub> ,<br>DISABLE = low |      | 106  | 135 |                   |

| (Includes Bias and Modulation Currents) | Icc                             | I <sub>BIAS</sub> = 1.5mA, I <sub>MOD</sub> = 3mA <sub>P-P</sub> ,<br>DISABLE = low |      | 55   | 70  | mA                |

|                                         |                                 | DISABLE = high                                                                      |      | 34   | 50  |                   |

| SIGNAL INPUT                            |                                 |                                                                                     |      |      |     |                   |

| Input Impedance                         |                                 | Single ended                                                                        | 42   | 50   | 58  | Ω                 |

| Input Sensitivity                       | V <sub>IN-MIN</sub>             | (Figure 2)                                                                          |      |      | 250 | mV <sub>P-P</sub> |

| Input Overload                          | V <sub>IN-MAX</sub>             | (Figure 2)                                                                          | 1000 |      |     | mV <sub>P-P</sub> |

| LASER MODULATION                        |                                 |                                                                                     |      |      |     |                   |

| Output Resistance                       | RT                              |                                                                                     | 42   | 50   | 58  | Ω                 |

| Minimum Modulation                      | IMOD-MIN                        |                                                                                     |      |      | 3   | mA                |

| Maximum Modulation                      | IMOD-MAX                        |                                                                                     | 12   |      |     | mA                |

| Modulation Current When DISABLE = High  |                                 | V <sub>IN</sub> = 1000mV <sub>P-P</sub> (Note 1)                                    |      | 100  | 250 | µАр₋р             |

| Voltage at OUT                          | Vout                            | (Note 2)                                                                            | 0.7  |      |     | V                 |

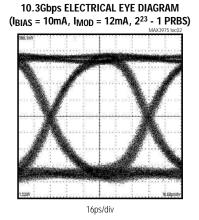

| Deterministic Jitter                    | DJ                              | (Notes 1, 3)                                                                        |      | 8    | 18  | psp₋p             |

| Random Jitter                           | RJ                              | (Note 1)                                                                            |      | 0.35 | 0.8 | psrms             |

| Output Switching Time                   | t <sub>R</sub> , t <sub>F</sub> | 20% to 80% (Notes 1, 4)                                                             |      | 28   | 36  | ps                |

| Current Gain from MODSET to OUT         |                                 |                                                                                     |      | 10   |     | mA/mA             |

| LASER BIAS                              |                                 |                                                                                     |      |      |     |                   |

| Minimum Bias Current                    | I <sub>BIAS-MIN</sub>           |                                                                                     |      |      | 1.5 | mA                |

| Maximum Bias Current                    | I <sub>BIAS-MAX</sub>           |                                                                                     | 10   |      |     | mA                |

| Current Gain from BIASSET to OUT        |                                 |                                                                                     |      | 10   |     | mA/mA             |

| Bias-Set Current Threshold for Disable  |                                 | (Note 5)                                                                            | 10   | 25   | _   | μΑ                |

| Output Current when Disabled            |                                 | I <sub>BIASSET</sub> ≤ 10μA or DISABLE = high                                       |      |      | 250 | μΑ                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.97 \text{V to } +3.63 \text{V}, R_{LOAD} = 50 \Omega, I_{MOD} + I_{BIAS} \leq \frac{(V_{CC} - V_{OUT\text{-}MIN} - 1.2 \text{V})}{50}, T_{A} = 0^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3 \text{V}, I_{BIAS} = 6.0 \text{mA}, I_{MOD} = 6.0 \text{mA}, \text{and } T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                               | SYMBOL           | CONDITIONS                           | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------|------------------|--------------------------------------|------|-----|------|-------|

| MONITOR OUTPUT                          |                  |                                      |      |     |      |       |

| MONITOR Gain                            |                  | $R_{MONITOR} = 1k\Omega$             |      | 16  |      | mA/mA |

| MONITOR Offset Error                    |                  |                                      | -25  |     | +25  | μΑ    |

| MONITOR Gain Variation                  |                  |                                      | -30  |     | +30  | %     |

| MONTOR Gain variation                   |                  | V <sub>CC</sub> and temperature only |      | ±8  |      | 70    |

| DISABLE INPUT                           |                  |                                      |      |     |      |       |

| Input High Voltage                      |                  |                                      | 2.0  |     |      | V     |

| Input Low Voltage                       |                  |                                      |      |     | 0.8  | V     |

| Input Resistance                        | R <sub>DIS</sub> |                                      | 50   | 76  | 100  | kΩ    |

| Input Current                           |                  | -0.3V < VDISABLE < (VCC + 0.3V)      | -100 |     | +100 | μΑ    |

| LASER CURRENT PROGRAMMIN                | NG               |                                      |      |     |      |       |

| Reference Voltage at BIASSET and MODSET | V <sub>BG</sub>  |                                      |      | 1.2 |      | V     |

| Gain Matching of IBIAS and IMOD         |                  | (Note 6)                             | -25  |     | +25  | %     |

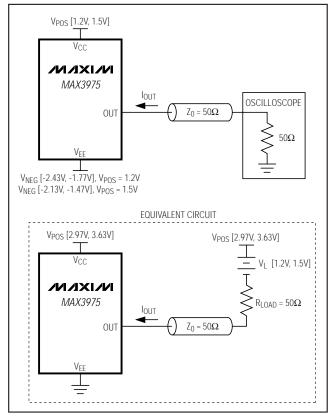

Note 1: Guaranteed by design and characterization using the circuit shown in Figure 1.

**Note 2:** V<sub>OUT</sub> is the minimum instantaneous voltage at the output (not the average voltage).

**Note 3:** Measured at 10.7Gbps with a pattern equivalent to  $2^{23}$  - 1 PRBS.

**Note 4:** Measured at 2.5Gbps with a 0101 repeating pattern.

Note 5: Programming a bias set current (IBIASSFT) below the threshold disables the output currents.

**Note 6:** Gain Matching = 100 x

$$\left(\frac{\text{Bias Gain}}{\text{Modulation Gain}} - 1\right)$$

Measured under the following conditions:

$I_{MOD} = 12mA$ ,  $I_{BIAS} = 4mA$

$I_{MOD} = 3mA$ ,  $I_{BIAS} = 4mA$

$I_{MOD} = I_{BIAS} = 4mA$

$I_{MOD} = I_{BIAS} = 8mA.$

VOLTAGE

V<sub>IN-</sub>

V<sub>IN-</sub>

V<sub>IN+</sub>

(V<sub>IN+</sub>) - (V<sub>IN-</sub>)

CURRENT

lout

| 125mV<sub>P-P</sub> MIN

| 500mV<sub>P-P</sub> MAX

| 125mV<sub>P-P</sub> MIN

| 1000mV<sub>P-P</sub> MAX

| 1000mV<sub>P-P</sub> MAX

Figure 2. Required Input Signal and Output Polarity

Figure 1. AC Characterization Circuit

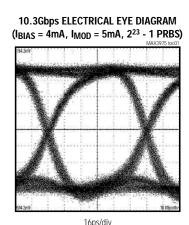

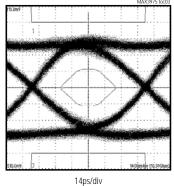

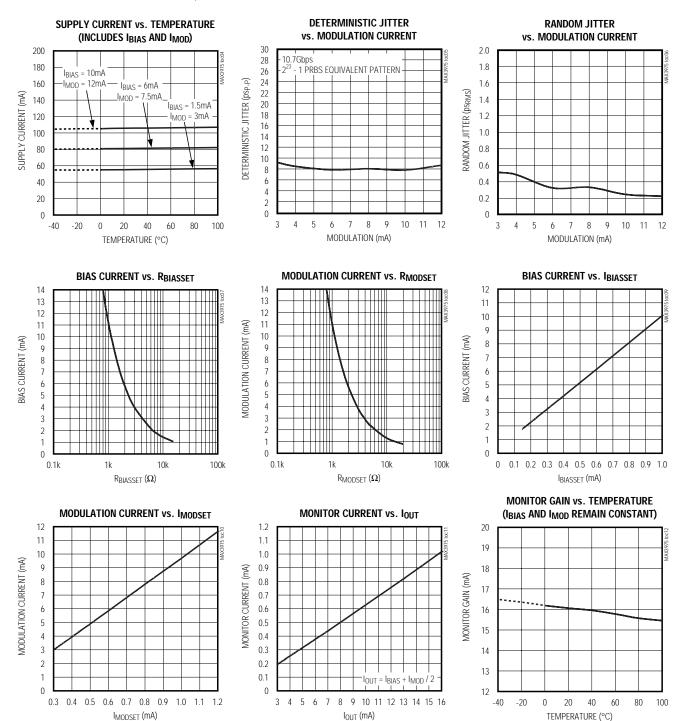

## Typical Operating Characteristics

$(V_{CC} = +2.97 \text{V to} +3.63 \text{V}, R_{LOAD} = 50\Omega, T_A = 0^{\circ}\text{C} \text{ to} +85^{\circ}\text{C}. \text{ Typical values are at V}_{CC} = +3.3 \text{V}, I_{BIAS} = 6.0 \text{mA}, I_{MOD} = 6.0 \text{mA}, and T_A = +25^{\circ}\text{C}, unless otherwise noted.)$

10.3Gbps OPTICAL EYE DIAGRAM

(PAVG = -2.0dBm, OMA = 471µWp.p, 2<sup>23</sup> - 1 PRBS)

(ADVANCED OPTICAL COMPONENTS VCSEL

TOSA HFE6190-561)

\*\*MAX3975 toc03\*\*

8GHz FILTER, 24% 10GbE MASK MARGIN

$T_A = +25$ °C, unless otherwise noted.)

$T_A = +25$ °C, unless otherwise noted.)

# Pin Description

| PIN                   | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                           |

|-----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, D1,<br>E1, E2     | V <sub>C</sub> C | +3.3V Supply Voltage. All V <sub>CC</sub> pins must be connected to the supply voltage.                                                                                                                                                                                                                            |

| A2                    | IN-              | Negative Data Input. Includes $50\Omega$ to $V_{CC}$ on-chip termination resistor.                                                                                                                                                                                                                                 |

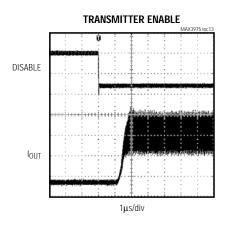

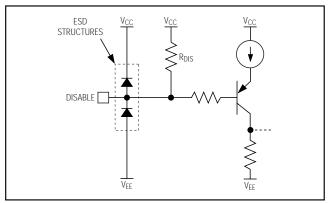

| A3                    | DISABLE          | Transmitter Disable, TTL Compatible. Total VCSEL current is low when this pin is set to a TTL high (asserted) or left open. VCSEL current is enabled when this input is set to a TTL low (deasserted).                                                                                                             |

| A4                    | IN+              | Positive Data Input. Includes $50\Omega$ to $V_{CC}$ on-chip termination resistor.                                                                                                                                                                                                                                 |

| A5, B1,<br>D5, E4, E5 | VEE              | Supply Ground. All V <sub>EE</sub> pins must be connected to the supply ground.                                                                                                                                                                                                                                    |

| B2, B4,<br>D2, D4     | N.C.             | No Connection. These pins must be soldered to the circuit board but should not be electrically connected to any circuit nodes (left floating).                                                                                                                                                                     |

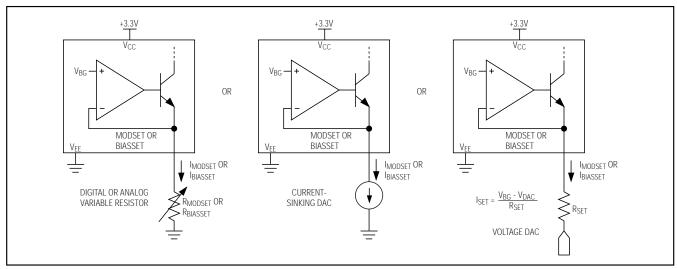

| B5                    | MODSET           | Modulation Current Set Pin, Analog. A resistor connected from this pin to V <sub>EE</sub> sets the desired modulation current. Modulation current can also be programmed with a current-sinking digital-to-analog converter (DAC) or voltage DAC with series resistor. See Figure 4.                               |

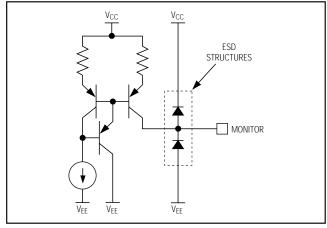

| C1                    | MONITOR          | VCSEL DC Current Monitor, Analog. Current from this output is proportional to the VCSEL DC current. Connect to V <sub>EE</sub> if not required in the application.                                                                                                                                                 |

| C5                    | BIASSET          | Bias Current Set Pin, Analog. A resistor connected from this pin to ground sets the desired bias current. Bias current can also be programmed with a current-sinking DAC or voltage DAC with series resistor. See Figure 4. Programming a current below the bias-set current threshold disables the driver output. |

| E3                    | OUT              | Modulation and Bias Current Output (Current Flows from VCSEL to OUT). Connect to VCSEL cathode.                                                                                                                                                                                                                    |

Figure 3. Functional Diagram

#### Detailed Description

The MAX3975 VCSEL driver consists of a high-speed modulator with programmable modulation and bias currents, transmitter disable circuit, and output-current monitor (Figure 3). The MAX3975 operates from a +3.3V supply and provides a  $50\Omega$  output termination, 3mA to 12mA of modulation, and 1.5mA to 10mA of bias current, allowing operation with a variety of 10Gbps VCSELs.

#### **Modulation Circuit**

The modulation circuitry consists of an input buffer, a current mirror, and a high-speed current switch. The modulator drives up to 12mA of modulation with a  $50\Omega$  VCSEL load.

The amplitude of the modulation current at OUT (I<sub>MOD</sub>) is linearly proportional to the control current at MODSET and is given by the relationship:

The control current is programmed with a resistor from MODSET to V<sub>EE</sub>. The control current can also be programmed with a current-sinking DAC or voltage DAC with series resistor as shown in Figure 4.

#### **Biasing Circuit**

The biasing circuitry consists of a current mirror that is connected to the driver output. Bias and modulation currents are combined internally, eliminating the need for an external bias inductor. The biasing circuit provides up to 10mA of bias current with a  $50\Omega$  VCSEL load.

The bias current at OUT (IBIAS) is linearly proportional to the control current at BIASSET and is given by the relationship:

IBIAS = IBIASSET X 10

The control current is programmed with a resistor from BIASSET to  $V_{EE}$ . The control current can also be programmed with a current-sinking DAC or voltage DAC with series resistor as shown in Figure 4. Programming a set current below the bias-set current threshold disables the driver output.

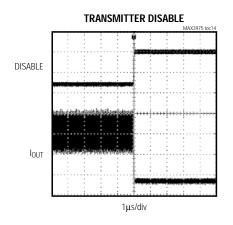

#### **Transmitter Disable**

The MAX3975 is equipped with a transmitter disable control (DISABLE). The DISABLE input is a TTL-compatible, low-current digital input. When DISABLE is set to TTL high (asserted) or left open, both the modulation and bias currents are disabled. The modulation and bias currents are enabled when DISABLE is set to TTL low (deasserted), and IBIASSET is above the disable threshold.

#### **Output Current Monitor**

The MONITOR is a current output that provides an indication of the VCSEL DC current. Connecting a resistor (RMONITOR) from the MONITOR output to VEE gives the following relationship:

VMONITOR =  $(1/16) \times (IBIAS + (IMOD / 2)) \times RMONITOR$ where, (IBIAS + (IMOD / 2)) = VCSEL DC current.

The voltage at the monitor output must be less than 2.18V for compliance. The recommended range for  $R_{MONITOR}$  is  $500\Omega$  to  $1.2k\Omega$ , with  $1k\Omega$  being typical. MONITOR must be connected to  $V_{FF}$  if not required in the application.

Figure 4. Bias and Modulation Current Controls

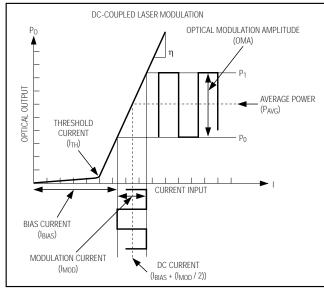

Table 1. Optical Power Relations

| PARAMETER                       | SYMBOL            | RELATION                                                                      |

|---------------------------------|-------------------|-------------------------------------------------------------------------------|

| Average Power                   | Pavg              | $P_{AVG} = (P_0 + P_1) / 2$                                                   |

| Extinction Ratio                | E <sub>r</sub>    | $E_{\Gamma} = P_1 / P_0$ $E_{\Gamma} = (2P_{AVG} + OMA) /$ $(2P_{AVG} - OMA)$ |

| Optical Power of a 1            | P <sub>1</sub>    | $P_1 = 2P_{AVG} E_r / (E_r + 1)$                                              |

| Optical Power of a 0            | P <sub>0</sub>    | $P_0 = 2P_{AVG} / (E_{\Gamma} + 1)$                                           |

| Optical Modulation<br>Amplitude | OMA               | OMA = $P_1 - P_0 = 2P_{AVG} (E_r - 1) / (E_r + 1)$                            |

| Laser Slope<br>Efficiency       | η                 | η = OMA / I <sub>MOD</sub>                                                    |

| Modulation Current              | IMOD              | I <sub>MOD</sub> = OMA / η                                                    |

| Bias Current                    | I <sub>BIAS</sub> | $I_{BIAS} = I_{TH} + (P_0 \times \eta)$                                       |

**Note:** Assuming a 50% average input duty cycle and mark density.

### Design Procedure

#### Interfacing with VCSELs

The MAX3975 modulating output (OUT) is optimized to interface directly to the cathode of a common-anode VCSEL. No external components are required between the VCSEL cathode and the driver output.

A  $50\Omega$  controlled-impedance transmission line with minimal length should be used between the VCSEL and the driver output. The VCSEL should be a high-speed, high-efficiency laser that requires low modulation current and generates a low voltage swing. Use a broadband supply filter at the VCSEL anode.

The minimum instantaneous voltage at OUT is 0.7V. To obtain fast edge transitions and low jitter, a VCSEL, supply voltage, and packaging technology must be selected that ensures V<sub>OUT</sub> is within the operating range of the driver output.

#### **Programming the Modulation Current**

For a desired optical modulation amplitude (OMA), the required modulation current can be calculated based on the laser slope efficiency ( $\eta$ ) using the equations in Table 1. To program the desired modulation current, connect a resistor from MODSET to VEE. See the Modulation Current vs. RMODSET graph in the *Typical Operating Characteristics* to select the value of RMODSET that corresponds to the required modulation current. When using an external DAC as shown in Figure 4, see the Modulation Current vs. IMODSET graph in the *Typical Operating Characteristics*.

Figure 5. Optical Power Relations

#### **Programming the Bias Current**

For a desired laser average optical power, PAVG, the required bias current can be calculated based on the laser slope efficiency  $(\eta)$  and threshold current (ITH) using the equations in Table 1. To program the desired bias current, connect a resistor from BIASSET to VEE. See the Bias Current vs. RBIASSET graph in the Typical Operating Characteristics to select the value of RBIASSET that corresponds to the required bias current. When using an external DAC as shown in Figure 4, see the Bias Current vs. IBIASSET graph in the Typical Operating Characteristics.

#### **Closed-Loop Operation**

Closed-loop power control can be implemented by using a controller IC as shown in the *Typical Application Circuit* on page 1. The controller IC monitors the photodiode current then adjusts the resistance/current seen by the BIASSET pin to maintain average power of the optical output over temperature and laser lifetime. Optical modulation amplitude (OMA) control is achieved by using a temperature indexed lookup table to control the resistance/current seen by the MODSET pin. The time constant from MODSET/BIASSET to OUT is typically 175ns.

#### Safety and Power Sequencing

For safety fault protection and proper power sequencing, use a low on-resistance MOSFET between the VCSEL power supply and the VCSEL anode, as shown in the *Typical Application Circuit*. A power-on-reset circuit and the safety fault signal of the controller IC (if applicable) should control the MOSFET gate.

The power-on-reset circuit should be designed to disable the VCSEL when the driver supply voltage is below 2.9V. This prevents the VCSEL from producing excessive optical output while the driver powers up/down.

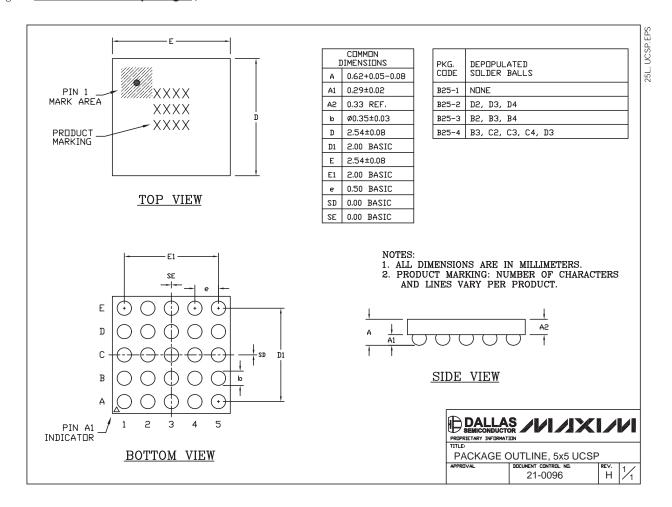

#### **UCSP Assembly Considerations**

The MAX3975 is packaged in a 2.5mm x 2.5mm, chipscale package (5 x 5 UCSP). Five of the solder ball positions (B3, C2, C3, C4, D3) are not populated (package code B25-4). For the latest application details on UCSP construction, dimensions, tape carrier information, PC board techniques, bump-pad layout, and rec-

Figure 6. Simplified DISABLE Input Structure

Figure 7. Simplified MONITOR Output Structure

ommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note: UCSP—A Wafer-Level Chip-Scale Package available on Maxim's website at www.maximic.com/ucsp.

#### \_Applications Information

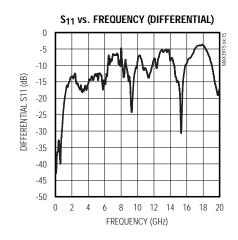

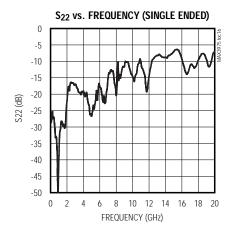

#### **Interface Models**

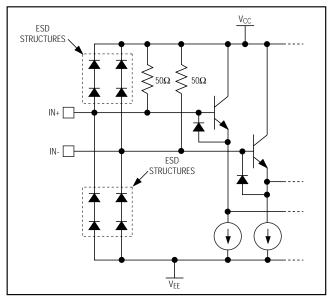

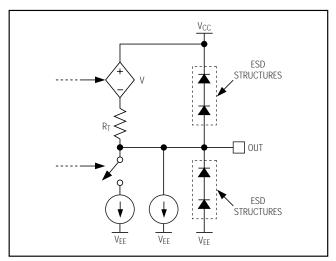

Figures 6, 7, 8, and 9 show simplified input and output circuits.

Figure 8. Simplified Data Input Structure

Figure 9. Simplified Data Output Structure

#### Layout Considerations

Design a broadband supply filter that provides low impedance between 10kHz and 15GHz. Use controlled-impedance transmission lines to interface to the high-speed input and output of the MAX3975. The parasitic capacitance at BIASSET and MODSET must be less than 20pF to ensure stability of the current controls.

| _Chip Informatio |

|------------------|

|------------------|

TRANSISTOR COUNT: 1387 PROCESS: SiGe Bipolar

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.